Project Description

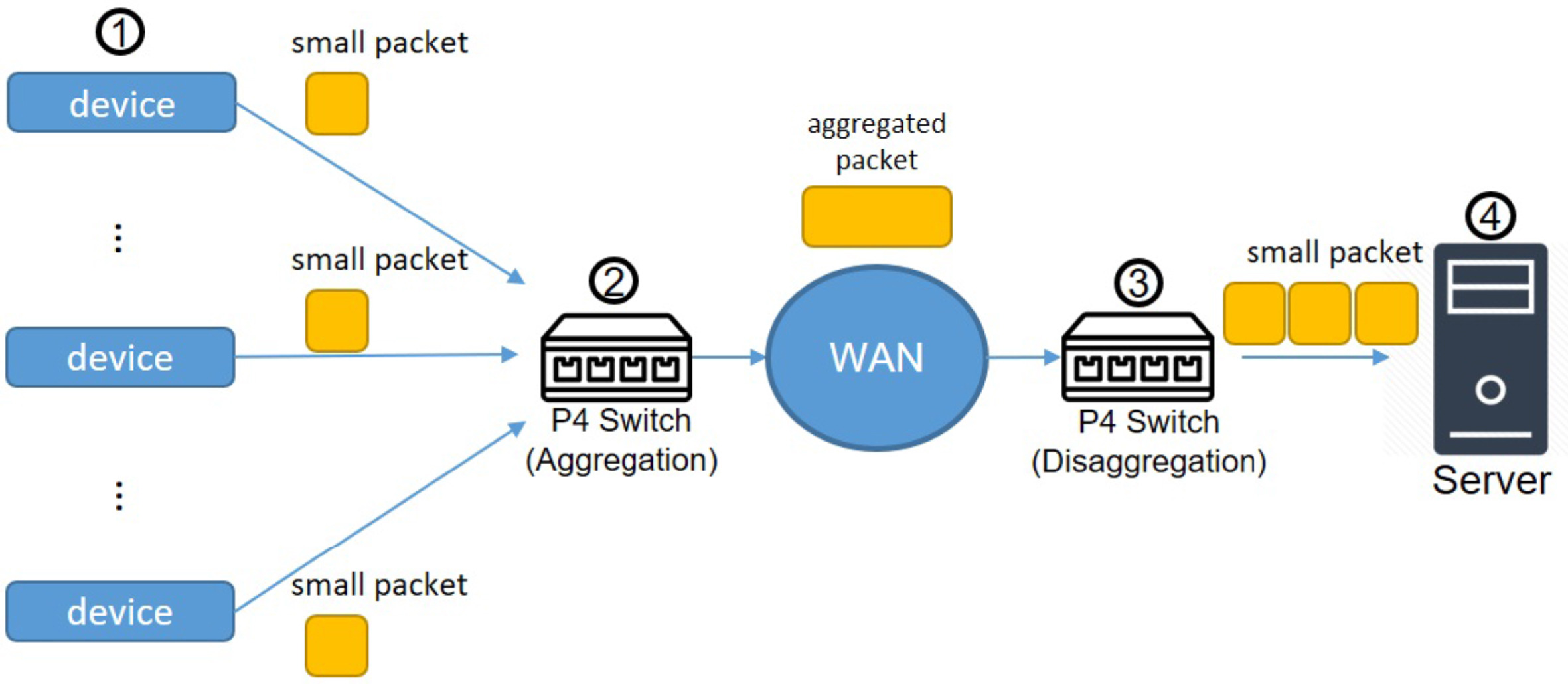

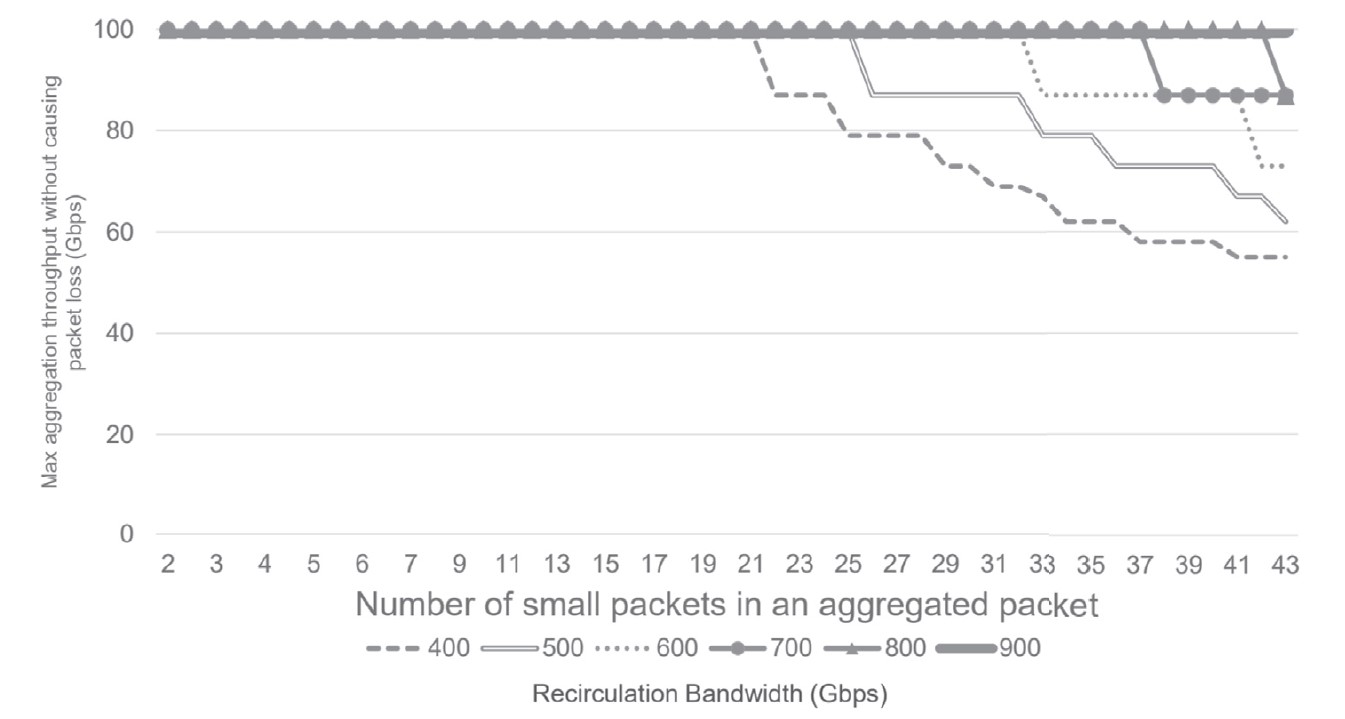

Aggregating multiple small packets into a large packet provides many advantages. For example, multiple small packets can share a single copy of common Ethernet/IP/UDP headers to reduce the percentage of network bandwidth spent on transmitting headers. In the past, packet aggregation and disaggregation were done by a server CPU or a switch CPU, resulting in low throughputs. In this paper, we design and implement packet aggregation and disaggregation functions in the packet processing pipelines of P4 switches. Our novel designs allow packets with various sizes of payload to be aggregated and disaggregated purely in the data plane of a P4 switch. Experimental results show that the achieved throughputs of our aggregation and disaggregation methods can reach 100 Gbps, which is the line rate of the used P4 switch.

- Propose a design to aggregate multiple small packets of various sizes into a large one in a P4 hardware switch

- Propose a design to disaggregate a large packet back to multiple original small packets in a P4 hardware switch

- Implement both designs in Tofino-based P4 hardware switches

- Experimental results show that the achieved throughputs of our aggregation and disaggregation methods can reach 100 Gbps, which is the line rate of the used P4 switch.

Team Members

Shie-Yuan Wang (shieyuan@cs.nctu.edu.tw)

Jun-Yi Li (gary841208c2@gmail.com)

Yi-Bing Lin (liny@nctu.edu.tw)

Open Source Code

Not available

Publications

- S.Y. Wang, J.Y. Li, and Y.B. Lin, “Aggregating and Disaggregating Packets with Various Sizes of Payload in P4 Switches at 100 Gbps Line Rate,” Journal of Network and Computer Applications, Vol. 165, September 1, 2020.

- S.Y. Wang, C.M. Wu, Y.B. Lin, and C.C. Huang, “High-Speed Data-Plane Packet Aggregation and Disaggregation by P4 Switches,” Journal of Network and Computer Applications, Vol. 142, pp. 98-110, 2019.

- Y.B. Lin, S.Y. Wang, C.C. Huang, and C.M. Wu, “The SDN Approach for Aggregation/Disaggregation of Sensor Data,” Sensors, 18(7), 2018.